# Tiger PCMCIA ATA Flash Card

## **Product Specification**

Version 1.7

August 2011

#### PRETEC/C-ONE Technology Corp.

Corporate Headquarters

8F, NO5, Lane 345, Yang Guang St., Neihu, Taipei, Taiwan

TEL: +886-2-2659-4380 Fax: +886-2-2659-4390

www.pretec.com

#### **Document Version**

| Version | Description                 | Description Date E |             | Approved by |

|---------|-----------------------------|--------------------|-------------|-------------|

| 1.0     | New issue                   | 19,Dec.,2008       | Amos Chung  | Matika Wang |

| 1.1     | Fix capacity type           | 15,Feb.,2009       | Matika Wang | David Lin   |

| 1.3     | Fix error correction bits   | 18,Mar.,2009       | Matika Wang | David Lin   |

| 1.4     | Update                      | 17,Dec.,2009       | Amos Chung  | Kent Liu    |

| 1.5     | 1.5 Modify performance      |                    | Amos Chung  | Kent Liu    |

| 1.6     | Modify capacity to 64GB     | 23, Aug., 2010     | Amos Chung  | Kent Liu    |

| 1.7     | Update vibration/shock data | 28, July., 2011    | Nelson Chen | Saber Lee   |

This document provides information regarding to Pretec Tiger PCMCIA ATA Flash Card product specification and is subject to change without any prior notice. No part in this report shall be distributed, reproduced, or disclosed in whole or in part without prior written permission of Pretec.

All rights reserved.

Pretec/C-ONE Technology Corp.

## **Contents**

| 1.1 GENERAL DESCRIPTION.       5         1.2 PEATURES.       5         1.3 PART NUMBER DEFINITION.       6         2. PRODUCT SPECIFICATION.       7         2.1 OPERATION AND ENVIRONMENT DESCRIPTION.       7         2.2 PHYSICAL DESCRIPTION.       7         3. SUPPORT FLASH MEDIA.       7         3.1 SUPPORTED NAND FLASH TYPE       7         3.1.1 Small block size of 16KB.       7         3.1.2 Large block size of 12RKB.       7         3.1.2 LOGICAL FORMAT PARAMETERS (CHS)       7         4. BLOCK DIAGRAM.       7         4.1 CONTROLLER ARCHITECTURE.       7         4.2 FLASH CARD ARCHITECTURE.       7         4.2 FLASH CARD ARCHITECTURE.       7         5. SPECIFICATION AND FEATURES.       7         5.1.1 Recommended Operating Conditions.       7         5.1.2 DC Electrical Characteristics for 5 Volts Operation.       7         5.1.3 DC Electrical Characteristics for 5 Volts Operation.       7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification.       7         5.1.6 Common Memory Write Timing Specification       7         5.1.9 I/O Input (Read) Timing Specification       7         5.1.10 True IDE Mode Timing Specification       7         5.1.10 Untu Blow Mod                                                                                                                                                 | 1. | INTRODUCTION                                    | 5 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------------|---|

| 2. PRODUCT SPECIFICATION         7           2.1 OPERATION AND ENVIRONMENT DESCRIPTION         7           2.2 PHYSICAL DESCRIPTION         7           3. SUPPORT FLASH MEDIA         7           3.1 SUPPORTED NAND FLASH TYPE         7           3.1.1 Small block size of 18KB         7           3.1.2 Large block size of 12KBR         7           3.2 LOGICAL FORMAT PARAMETERS (CHS)         7           4. BLOCK DIAGRAM         7           4.1 CONTROLLER ARCHITECTURE         7           4.2 FLASH CARD ARCHITECTURE         7           4.2 FLASH CARD ARCHITECTURE         7           5.1 RECOMMENDED Operating Conditions         7           5.1.2 DC Electrical Characteristics for 5 Volts Operation         7           5.1.3 DC Electrical Characteristics for 5 Volts Operation         7           5.1.4 Attribute Memory Read Timing Specification         7           5.1.5 Configuration Register (Attribute Memory) Write Timing Specification         7           5.1.6 Common Memory Read Timing Specification         7           5.1.7 Common Memory Write Timing Specification         7           5.1.9 I/O Input (Read) Timing Specification         7           5.1.10 True IDE Mode PIO (ReadWrite) Timing Specification         7           5.1.11 True IDE Multiword DMA Mode I/O (ReadWrite)                                                                    |    | 1.2 FEATURES                                    | 5 |

| 2.1 OPERATION AND ENVIRONMENT DESCRIPTION.       7         2.2 PHYSICAL DESCRIPTION.       7         3. SUPPORT FLASH MEDIA       7         3.1 SUPPORTED NAND FLASH TYPE       7         3.1.1 Small block size of 18KB.       7         3.1.2 Large block size of 128KB.       7         3.2. LOGICAL FORMAT PRAMETERS (CHS)       7         4. BLOCK DIAGRAM.       7         4.1 CONTROLLER ARCHITECTURE.       7         4.2 FLASH CARD ARCHITECTURE.       7         5. SPECIFICATION AND FEATURES       7         5.1 ELECTRICAL SPECIFICATION.       7         5.1.1 Recommended Operating Conditions.       7         5.1.2 DC Electrical Characteristics for 5 Volts Operation.       7         5.1.3 DC Electrical Characteristics for 5.3 Volts Operation.       7         5.1.4 Attribute Memory Read Timing Specification.       7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification.       7         5.1.6 Common Memory Read Timing Specification.       7         5.1.7 Common Memory Read Timing Specification.       7         5.1.8 I/O Input (Write) Timing Specification.       7         5.1.9 Up Input (Write) Timing Specification.       7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification.       7         5.1                                                                                                              |    |                                                 |   |

| 2.2 PHYSICAL DESCRIPTION.       7         3. SUPPORT FLASH MEDIA.       7         3.1.1 Small block size of 16KB.       7         3.1.2 Large block size of 128KB.       7         3.1.2 Large block size of 128KB.       7         3.1.2 Large block size of 128KB.       7         3.1.2 Lorgical Format Parameters (CHS)       7         4. BLOCK DIAGRAM.       7         4.1 CONTROLLER ARCHITECTURE.       7         4.2 FLASH CARD ARCHITECTURE.       7         5. SPECIFICATION AND FEATURES       7         5.1.1 Recommended Operating Conditions.       7         5.1.2 LECTRICAL SPECIFICATION.       7         5.1.3 DC Electrical Characteristics for 5 Volts Operation.       7         5.1.4 Attribute Memory Read Timing Specification.       7         5.1.5 Common Memory Read Timing Specification.       7         5.1.6 Common Memory Read Timing Specification.       7         5.1.7 Common Memory Write Timing Specification.       7         5.1.8 I/O Input (Read) Timing Specification.       7         5.1.9 Input (Write) Timing Specification.       7         5.1.10 True IDE Mode PIO (ReadWrite) Timing Specification.       7         5.1.11 True IDE PIO Mode Timing Diagram.       7         5.1.12 True IDE Multiword DMA Mode Read/Write Timing Speci                                                                                                              | 2. | PRODUCT SPECIFICATION                           | 7 |

| 3.1 SUPPORTED NAND FLASH TYPE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |                                                 |   |

| 3.1.1 Small block size of 16kB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3. | SUPPORT FLASH MEDIA                             | 7 |

| 3.1.1 Small block size of 16kB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 3.1 SUPPORTED NAND FLASH TYPE                   | 7 |

| 3.2 LOGICAL FORMAT PARAMETERS (CHS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |                                                 |   |

| 4. BLOCK DIAGRAM       7         4.1 CONTROLLER ARCHITECTURE       7         4.2 FLASH CARD ARCHITECTURE       7         5. SPECIFICATION AND FEATURES       7         5.1 ELECTRICAL SPECIFICATION       7         5.1.1 Recommended Operating Conditions       7         5.1.2 DC Electrical Characteristics for 5 Volts Operation       7         5.1.3 DC Electrical Characteristics for 3.3 Volts Operation       7         5.1.4 Attribute Memory Read Timing Specification       7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       7         5.1.6 Common Memory Read Timing Specification       7         5.1.7 Common Memory Write Timing Specification       7         5.1.8 I/O Input (Read) Timing Specification       7         5.1.9 I/O Input (Write) Timing Specification       7         5.1.10 True IDE Mode Timing Diagram       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Specification       7         5.1.15 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Requirements       7         5.1.16 Sustained Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Host Pause Timing       7 <td></td> <td></td> <td></td>                       |    |                                                 |   |

| 4.1 CONTROLLER ARCHITECTURE       7         4.2 FLASH CARD ARCHITECTURE       7         5. SPECIFICATION AND FEATURES       7         5.1 RECTRICAL SPECIFICATION       7         5.1.1 Recommended Operating Conditions       .7         5.1.2 DC Electrical Characteristics for 5 Volts Operation       .7         5.1.3 DC Electrical Characteristics for 3.3 Volts Operation       .7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       .7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       .7         5.1.6 Common Memory Read Timing Specification       .7         5.1.7 Common Memory Write Timing Specification       .7         5.1.8 I/O Input (Read) Timing Specification       .7         5.1.9 I/O Input (Write) Timing Specification       .7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       .7         5.1.11 True IDE PIO Mode Timing Diagram       .7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       .7         5.1.14 Ultra DMA Data Burst Timing Requirements       .7         5.1.15 Ultra DMA Data Burst Timing Requirements       .7         5.1.16 Sustained Ultra DMA Data-In Burst Host Pause Timing       .7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       .7                                                 |    | 3.2 LOGICAL FORMAT PARAMETERS (CHS)             | 7 |

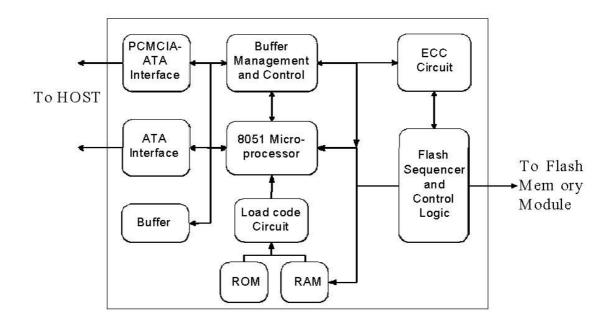

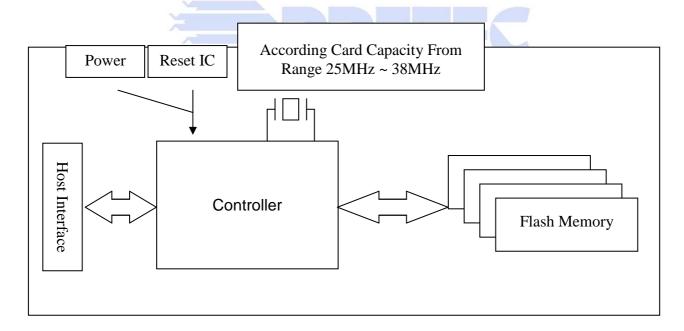

| 4.2 FLASH CARD ARCHITECTURE       7         5. SPECIFICATION AND FEATURES       7         5.1 ELECTRICAL SPECIFICATION       7         5.1.1 Recommended Operating Conditions       .7         5.1.2 DC Electrical Characteristics for 5 Volts Operation       .7         5.1.3 DC Electrical Characteristics for 3.3 Volts Operation       .7         5.1.4 Attribute Memory Read Timing Specification       .7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       .7         5.1.6 Common Memory Read Timing Specification       .7         5.1.7 Common Memory Write Timing Specification       .7         5.1.8 I/O Input (Read) Timing Specification       .7         5.1.9 I/O Input (Write) Timing Specification       .7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       .7         5.1.11 True IDE PIO Mode Timing Diagram       .7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       .7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       .7         5.1.14 Ultra DMA Data Burst Timing Requirements       .7         5.1.15 Ultra DMA Data Burst Host Pause Timing       .7         5.1.16 Sustained Ultra DMA Data-In Burst Host Timing       .7         5.1.19 Ultra DMA Data-In Burst Device Termination Timing       .7                                        | 4. | BLOCK DIAGRAM                                   | 7 |

| 4.2 FLASH CARD ARCHITECTURE       7         5. SPECIFICATION AND FEATURES       7         5.1 ELECTRICAL SPECIFICATION       7         5.1.1 Recommended Operating Conditions       .7         5.1.2 DC Electrical Characteristics for 5 Volts Operation       .7         5.1.3 DC Electrical Characteristics for 3.3 Volts Operation       .7         5.1.4 Attribute Memory Read Timing Specification       .7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       .7         5.1.6 Common Memory Read Timing Specification       .7         5.1.7 Common Memory Write Timing Specification       .7         5.1.8 I/O Input (Read) Timing Specification       .7         5.1.9 I/O Input (Write) Timing Specification       .7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       .7         5.1.11 True IDE PIO Mode Timing Diagram       .7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       .7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       .7         5.1.14 Ultra DMA Data Burst Timing Requirements       .7         5.1.15 Ultra DMA Data Burst Host Pause Timing       .7         5.1.16 Sustained Ultra DMA Data-In Burst Host Timing       .7         5.1.19 Ultra DMA Data-In Burst Device Termination Timing       .7                                        |    | 4.1 CONTROLLER ARCHITECTURE                     | 7 |

| 5. SPECIFICATION AND FEATURES       7         5.1 ELECTRICAL SPECIFICATION       7         5.1.1 Recommended Operating Conditions       7         5.1.2 DC Electrical Characteristics for 5 Volts Operation       7         5.1.3 DC Electrical Characteristics for 3.3 Volts Operation       7         5.1.4 Attribute Memory Read Timing Specification       7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       7         5.1.7 Common Memory Read Timing Specification       7         5.1.7 Common Memory Write Timing Specification       7         5.1.8 I/O Input (Read) Timing Specification       7         5.1.9 I/O Input (Write) Timing Specification       7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       7         5.1.11 True IDE PIO Mode Timing Diagram       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Requirements       7         5.1.16 Sustained Ultra DMA Data-In Burst Timing       7         5.1.19 Ultra DMA Data-In Burst Host Fermination Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7                       |    |                                                 |   |

| 5.1 ELECTRICAL SPECIFICATION       7         5.1.1 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _  |                                                 |   |

| 5.1.1 Recommended Operating Conditions       .7         5.1.2 DC Electrical Characteristics for 5 Volts Operation       .7         5.1.3 DC Electrical Characteristics for 3.3 Volts Operation       .7         5.1.4 Attribute Memory Read Timing Specification       .7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       .7         5.1.6 Common Memory Read Timing Specification       .7         5.1.7 Common Memory Write Timing Specification       .7         5.1.8 I/O Input (Read) Timing Specification       .7         5.1.9 Vol Input (Write) Timing Specification       .7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       .7         5.1.11 True IDE PIO Mode Timing Diagram       .7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       .7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       .7         5.1.14 Ultra DMA Data Burst Timing Requirements       .7         5.1.15 Ultra DMA Data Burst Timing Descriptions       .7         5.1.16 Sustained Ultra DMA Data-In Burst Host Pause Timing       .7         5.1.19 Ultra DMA Data-In Burst Host Pause Timing       .7         5.1.20 Ultra DMA Data-In Burst Host Termination Timing       .7         5.1.21 Sustained Ultra DMA Data-Out Burst Host Termination Timing       .7         5.1.22     | Э. |                                                 |   |

| 5.1.2 DC Electrical Characteristics for 3.3 Volts Operation       7         5.1.3 DC Electrical Characteristics for 3.3 Volts Operation       7         5.1.4 Attribute Memory Read Timing Specification       7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       7         5.1.6 Common Memory Read Timing Specification       7         5.1.7 Common Memory Write Timing Specification       7         5.1.8 I/O Input (Read) Timing Specification       7         5.1.9 I/O Input (Write) Timing Specification       7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       7         5.1.11 True IDE PIO Mode Timing Diagram       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.15 Ultra DMA Data Burst Timing Requirements       7         5.1.16 Ultra DMA Data Burst Timing Descriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Host Pause Timing       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Host Termination Timing       7         5.2 Po     |    |                                                 |   |

| 5.1.3 DC Electrical Characteristics for 3.3 Volts Operation.       7         5.1.4 Attribute Memory Read Timing Specification.       7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification.       7         5.1.6 Common Memory Read Timing Specification.       7         5.1.7 Common Memory Write Timing Specification.       7         5.1.8 I/O Input (Read) Timing Specification.       7         5.1.9 I/O Input (Write) Timing Specification.       7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification.       7         5.1.11 True IDE Mode PIO Mode Timing Diagram.       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification.       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram.       7         5.1.15 Ultra DMA Data Burst Timing Requirements.       7         5.1.15 Ultra DMA Data Burst Timing Descriptions.       7         5.1.16 Sustained Ultra DMA Data-In Burst Timing Descriptions.       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing.       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing.       7         5.1.20 Ultra DMA Data-In Burst Host Initiation Timing.       7         5.1.21 Ultra DMA Data-Out Burst Host Initiation Timing.       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing.       7         < |    |                                                 |   |

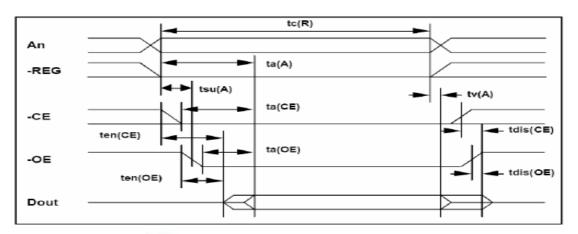

| 5.1.4 Attribute Memory Read Timing Specification       7         5.1.5 Configuration Register (Attribute Memory) Write Timing Specification       7         5.1.6 Common Memory Read Timing Specification       7         5.1.7 Common Memory Write Timing Specification       7         5.1.8 I/O Input (Read) Timing Specification       7         5.1.9 I/O Input (Write) Timing Specification       7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       7         5.1.11 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data-In Burst Timing       7         5.1.16 Sustained Ultra DMA Data-In Burst Timing       7         5.1.17 Ultra DMA Data-In Burst Device Termination Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Host Termination Timing       7         5.2     |    |                                                 |   |

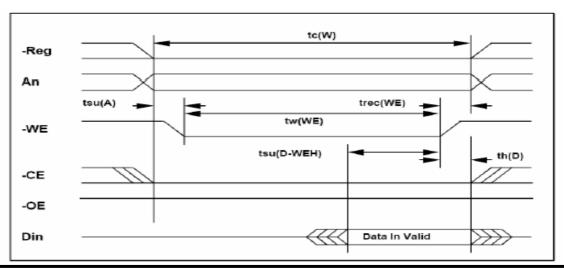

| 5.1.5 Configuration Régister (Attribute Memory) Write Timing Specification       7         5.1.6 Common Memory Read Timing Specification       7         5.1.7 Common Memory Write Timing Specification       7         5.1.8 I/O Input (Read) Timing Specification       7         5.1.9 I/O Input (Write) Timing Specification       7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       7         5.1.11 True IDE Mode Fining Diagram       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Requirements       7         5.1.16 Sustained Ultra DMA Data-In Burst Poscriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Host Pause Timing       7         5.1.19 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Host Termination Timing       7         5.2 Power Mana     |    |                                                 |   |

| 5.1.6 Common Memory Read Timing Specification       7         5.1.7 Common Memory Write Timing Specification       7         5.1.8 I/O Input (Read) Timing Specification       7         5.1.9 I/O Input (Write) Timing Specification       7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       7         5.1.11 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Descriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Timing       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.20 Ultra DMA Data-In Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Host Termination Timing       7         5.2 Power ManaGement       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION                                        |    |                                                 |   |

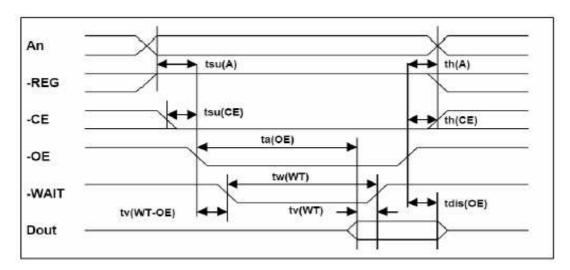

| 5.1.7 Common Memory Write Timing Specification       7         5.1.8 I/O Input (Read) Timing Specification       7         5.1.9 I/O Input (Write) Timing Specification       7         5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       7         5.1.11 True IDE PIO Mode Timing Diagram       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Descriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 Power MANAGEMENT       7         5.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         7. PIN ASSIGNMENT                                                  |    | 5.1.6 Common Memory Read Timing Specification   | 7 |

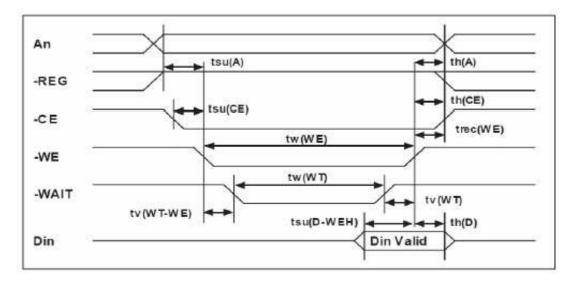

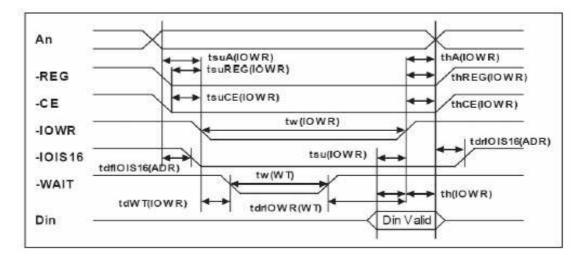

| 5.1.9 I/O Input (Write) Timing Specification       7         5.1.10 True IDE Mode PIO (ReadWrite) Timing Specification       7         5.1.11 True IDE PIO Mode Timing Diagram       7         5.1.12 True IDE Multiword DMA Mode I/O (ReadWrite) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Descriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Timing       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6. PHYSICAL SPECIFICATION       7         7. PIN ASSIGNMENT       7         7. SI                                                                           |    | 5.1.7 Common Memory Write Timing Specification  | 7 |

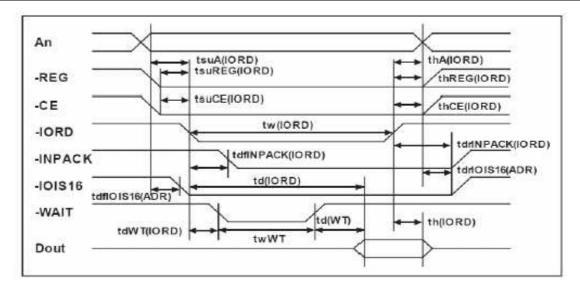

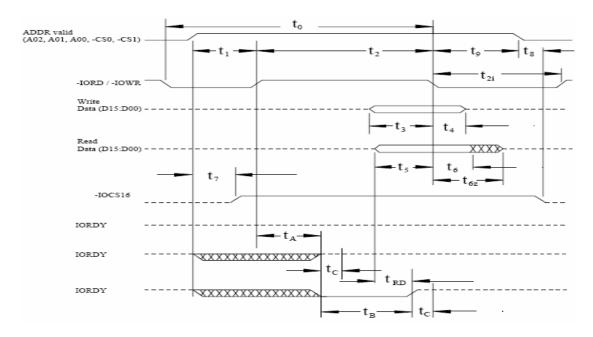

| 5.1.10 True IDE Mode PIO (Read/Write) Timing Specification       7         5.1.11 True IDE PIO Mode Timing Diagram       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification.       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.14 Ultra DMA Data Burst Timing Requirements.       7         5.1.15 Ultra DMA Data Burst Timing Descriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Timing       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Host Permination Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 Power MANAGEMENT       7         5.2.1 Normal Mode       7         6. PHYSICAL SPECIFICATION       7         6. PHYSICAL SPECIFICATION       7         7. PIN ASSIGNMENT       7         7. 2 SIGNAL DESCRIPTION       7                                                                                                                                                           |    | 5.1.8 I/O Input (Read) Timing Specification     | 7 |

| 5.1.11 True IDE PIO Mode Timing Diagram       7         5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification       7         5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Descriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Host Pause Timing       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.24 Ultra DMA Data-Out Burst Device Termination Timing       7         5.1.25 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         7. PIN ASSIGNMENT       7         7. 2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                            |    |                                                 |   |

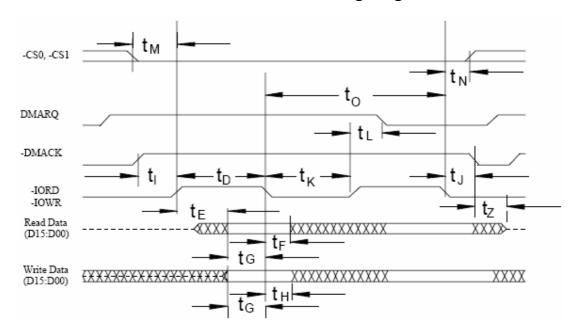

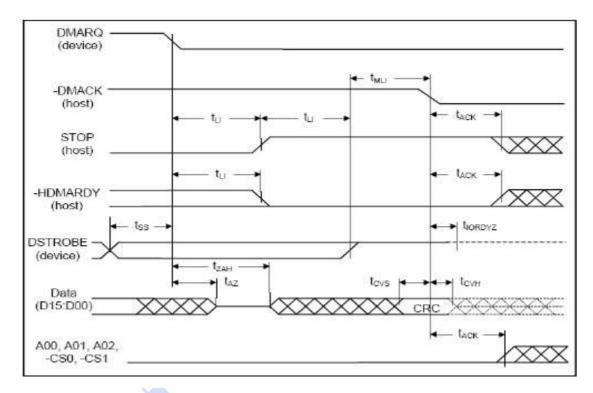

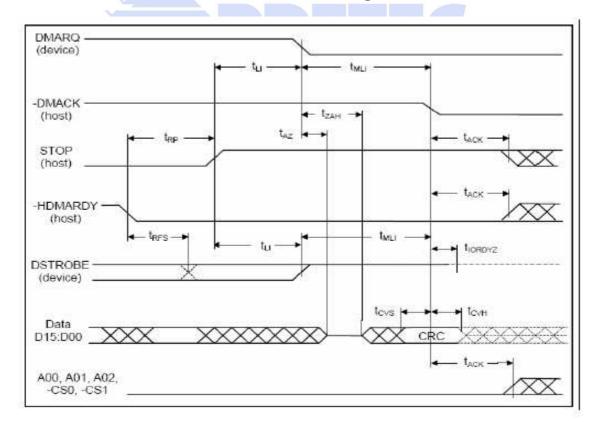

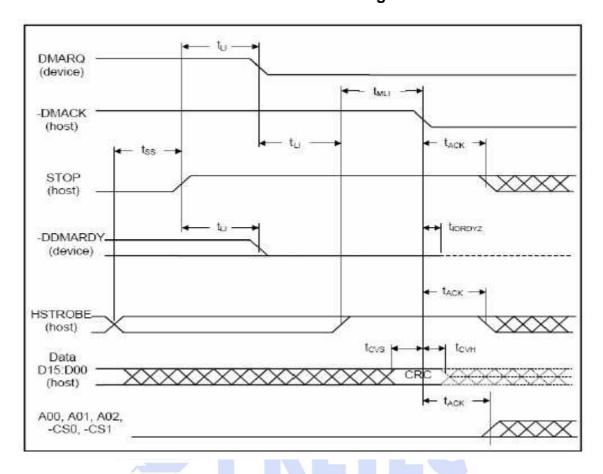

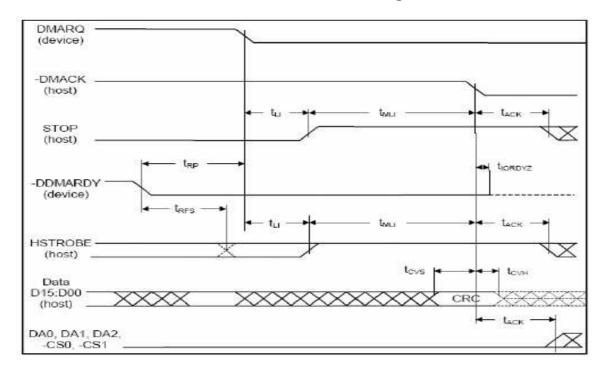

| 5.1.12 True IDE Multiword DMA Mode I/O (Read/Write) Timing Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                                                 |   |

| 5.1.13 True IDE Multiword DMA Mode Read/Write Timing Diagram       7         5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Descriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Timing       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Device Termination Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.1.29 OWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIAATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                  |    |                                                 |   |

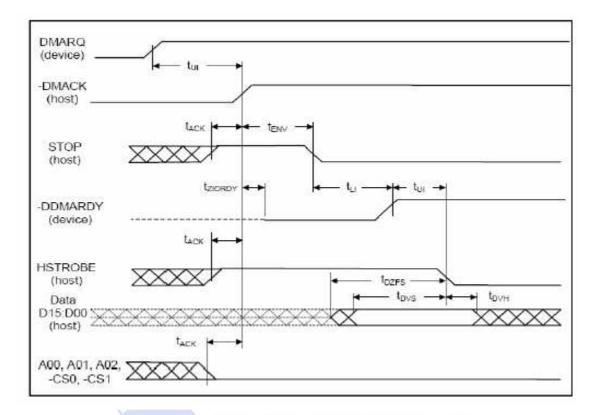

| 5.1.14 Ultra DMA Data Burst Timing Requirements       7         5.1.15 Ultra DMA Data Burst Timing Descriptions       7         5.1.16 Sustained Ultra DMA Data-In Burst Timing       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Device Termination Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                |    |                                                 |   |

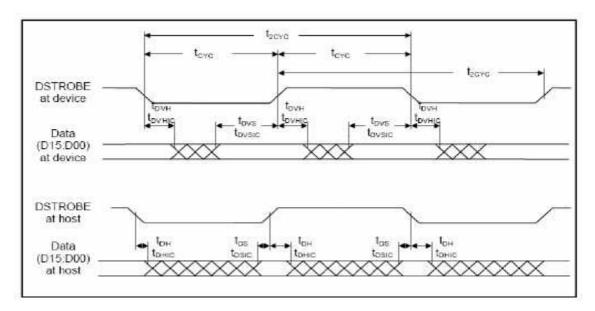

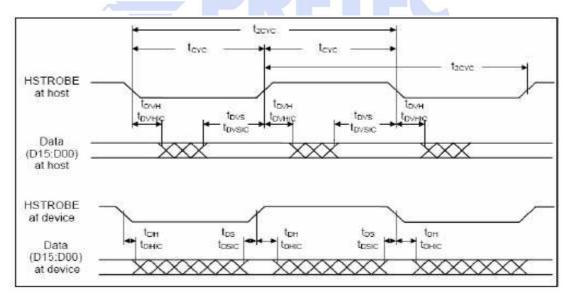

| 5.1.16 Sustained Ultra DMA Data-In Burst Timing       7         5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Device Termination Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6. PHYSICAL SPECIFICATION       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                                 |   |

| 5.1.17 Ultra DMA Data-In Burst Host Pause Timing       7         5.1.18 Ultra DMA Data-In Burst Device Termination Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 5.1.15 Ultra DMA Data Burst Timing Descriptions | 7 |

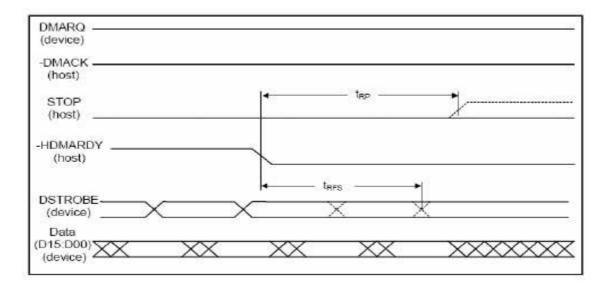

| 5.1.18 Ultra DMA Data-In Burst Device Termination Timing       7         5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |                                                 |   |

| 5.1.19 Ultra DMA Data-In Burst Host Termination Timing       7         5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |                                                 |   |

| 5.1.20 Ultra DMA Data-Out Burst Host Initiation Timing       7         5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |                                                 |   |

| 5.1.21 Sustained Ultra DMA Data-Out Burst Timing       7         5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                                 |   |

| 5.1.22 Ultra DMA Data-Out Burst Host Termination Timing       7         5.1.23 Ultra DMA Data-Out Burst Device Termination Timing       7         5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |                                                 |   |

| 5.2 POWER MANAGEMENT       7         5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |                                                 |   |

| 5.2.1 Normal Mode       7         5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                                 |   |

| 5.2.2 Power Down Mode       7         6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                                                 |   |

| 6. PHYSICAL SPECIFICATION       7         6.1 PCMCIA ATA (TYPE II)       7         7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |                                                 |   |

| 6.1 PCMCIA ATA (TYPE II)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |                                                 |   |

| 7. PIN ASSIGNMENT       7         7.1 PCMCIA ATA       7         7.2 SIGNAL DESCRIPTION       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6. |                                                 |   |

| 7.1 PCMCIA ATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 6.1 PCMCIA ATA (TYPE II)                        | 7 |

| 7.2 SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7. | PIN ASSIGNMENT                                  | 7 |

| 7.2 SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 7.1 PCMCIA ATA                                  | 7 |

| 8. CIS AND FUNCTIONS CONFIGURATION REGISTERS7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |                                                 |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8. | CIS AND FUNCTIONS CONFIGURATION REGISTERS       | 7 |

| 7<br>7                            |

|-----------------------------------|

| 7                                 |

|                                   |

| 7                                 |

| 7                                 |

| 7                                 |

|                                   |

| 7                                 |

| 7<br>7                            |

| 7<br>7                            |

| 7<br>7                            |

| 7                                 |

| 7                                 |

| 7                                 |

| 7                                 |

| 7                                 |

| 7                                 |

| 7                                 |

| 7                                 |

| 7                                 |

| 7                                 |

| 7<br>7                            |

|                                   |

| 7                                 |

| 7                                 |

| /                                 |

| 7<br>7                            |

|                                   |

| 7<br>7                            |

| 7<br>7<br><b>7</b>                |

| 7<br>7<br>7                       |

| 7<br><b>7</b><br>7<br>7           |

| 7<br>7<br>7<br>7<br>7             |

| 7 7 7 7 7 7 7                     |

| 7 7 7 7 7 7 7                     |

| 7 7 7 7 7 7 7                     |

| 7 7 7 7 7 7 7 7 7                 |

| 7 7 7 7 7 7 7                     |

| 7 7 7 7 7 7 7 7 7 7               |

| 7 7 7 7 7 7 7 7 7 7 7 7 7         |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7   |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7       |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7     |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7     |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7     |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 |

|                                   |

#### 1. Introduction

#### 1.1 General Description

Pretec Tiger PCMCIA ATA Flash Card uses NAND-Type flash memory devices, which leads to its remarkable high performance and comes with capacities from 128 MB to 64GB unformatted.

Compliant with ISA (Industrial Standard Architecture) bus interface standard, the Tiger PCMCIA ATA Flash Card performs sequential read/write for each sector (512 bytes) count. It also conforms to PCMCIA specification and is designed with precision mechanics to enable host devices to read/write from the PCMCIA interface into flash media. It can operate with a 3.3V or 5V single power from the host side.

The card provides extraordinary memory medium for PC or any other electric equipment and digital still camera, and, in particular, Pretec Tiger PCMCIA ATA Flash Card has been approved through various compatibility tests to be used in numerous portable desktop, notebook computers and handheld PCs and auto PCs under industrial environment.

#### 1.2 Features

■ PC Card compliant

Conforms to CompactFlash standard

Compatible with PCMCIA ATA specification

Compatible with all PC Card Services and Socket Services

- PCMCIA ATA / IDE interface

- ATA command set compatible

Support for 8-bit or 16-bit host data transfer

- Extremely rugged and reliable

- Advanced defect block management

- Support background erased operation

- **Dynamic Wear-Leveling**

- Power cycling test passed

- 3.3/5 Volt power supply, very low power consumption

- Zero-power data retention, no batteries required

- Internal self-diagnostic program operates at VCC power on

- Auto sleep mode

- High reliability based on internal ECC (Error Correcting Code) function

- Automatic on-the-fly, in-buffer error correction

- •Error Correction of 4 bits random error per sector

- 3 variations of mode access

- Memory card mode

- I/O card mode

- •True IDE mode

- -PIO up to Mode 6

- -UDMA up to mode 5

## 1.3 Part Number Definition

#### $X_1X_2 X_3 X_4X_5 X_6 X_7 X_8$

| Code                                         | Definition           | symbol | Description                 |  |  |

|----------------------------------------------|----------------------|--------|-----------------------------|--|--|

| X <sub>1</sub> X <sub>2</sub>                | Card Type            | PA     | PCMCIA Type II              |  |  |

| X <sub>3</sub>                               | Solution             | М      | Tiger Series                |  |  |

|                                              |                      | 128    | 128MB                       |  |  |

|                                              |                      | 256    | 256MB                       |  |  |

|                                              |                      | 512    | 512MB                       |  |  |

|                                              |                      | 01G    | 1GB                         |  |  |

| X <sub>4</sub> X <sub>5</sub> X <sub>6</sub> |                      | 02G    | 2GB                         |  |  |

|                                              | Capacity             | 04G    | 4GB                         |  |  |

|                                              |                      | 06G    | 6GB                         |  |  |

|                                              |                      | 08G    | 8GB                         |  |  |

|                                              |                      | 16G    | 16GB                        |  |  |

|                                              |                      | 32G    | 32GB                        |  |  |

|                                              |                      | 64G    | 64GB                        |  |  |

|                                              |                      | С      | Commercial Grade 0°C ~ 70°C |  |  |

| X <sub>7</sub>                               | Temperature<br>Range |        | Light Grade -20°C ~ +85°C   |  |  |

|                                              | rango                | Н      | Heavy Grade -40°C ~ +85°C   |  |  |

| V                                            | Hausian              | Р      | Plastic housing             |  |  |

| X <sub>8</sub>                               | Housing              | R      | Metal housing               |  |  |

## 2. Product Specification

## 2.1 Operation and environment description

| Operating Voltage          | DC Input Power          | 5V                             | ± 10%          |  |

|----------------------------|-------------------------|--------------------------------|----------------|--|

| Operating voltage          | Do input i owei         | 3.3V ± 5%                      |                |  |

|                            |                         | Read Mode: 84mA                |                |  |

|                            | 5V                      | Write Mode: 96mA               |                |  |

| Typical Power              |                         | Standby Mode: 9.3m             | A              |  |

| Consumptions               |                         | Read Mode: 80mA                |                |  |

|                            | 3.3V                    | Write Mode: 75mA               |                |  |

|                            |                         | Standby Mode: 1.1m             | A              |  |

|                            | Operating Tomporature   | Extended Temp.                 | -20°C to +85°C |  |

|                            | Operating Temperature   | Industrial Temp.               | -40°C to +85°C |  |

|                            | Storage Temperature     | Extended Temp.                 | -40°C to +90°C |  |

|                            | Storage remperature     | Industrial Temp.               | -50°C to +90°C |  |

| 7                          | Humidity Operation      | 5% to 95% (Non-condensing)     |                |  |

|                            | Humidity Non-operation  | 5% to 95% (Non-condensing)     |                |  |

| Environment                | Shock Operation         | Plastic Housing                | 50-G (Max)     |  |

| Conditions                 | Shock Operation         | Material Housing               | 1500-G (Max)   |  |

|                            | Shock Non-Operation     | Plastic Housing                | 50-G (Max)     |  |

|                            | Shock Non-Operation     | Material Housing               | 1500-G (Max)   |  |

|                            | Vibration Operation     | 20-G (Peak to peak to maximum) |                |  |

|                            | Vibration Non-operation | 20-G (Peak to peak to maximum) |                |  |

| Operation System supported | DOS, W                  | indows 98/ME/NT/2000           | )/XP           |  |

|                            |                         |                                |                |  |

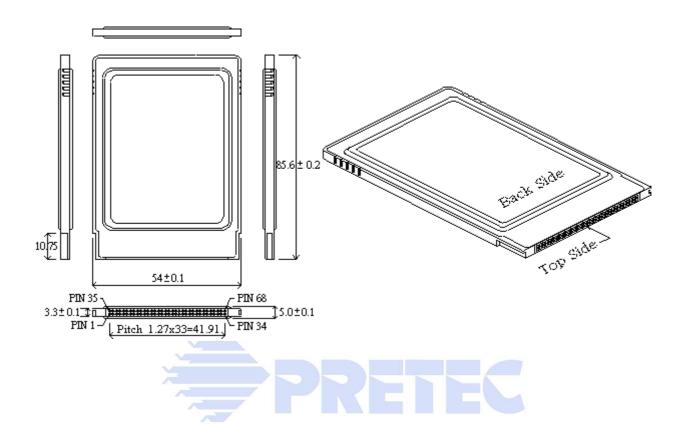

## 2.2 Physical description

| Measures           | Type II             | L x W x H<br>85.6 x 54 x 5.0 (mm)                |

|--------------------|---------------------|--------------------------------------------------|

| Storage Capacities | Capacity            | 128MB – 64GB                                     |

| Performance        | Data Transfer Rates | Read: 35 Mbytes/sec                              |

| renormance         | Data Transfer Rates | Write: 20 Mbytes/sec                             |

|                    | MTBF                | 3,000,000 hours                                  |

| Reliability        | Error Correction    | More than 4 bit error correction per second read |

|                    | R/W Test            | Test disk: 3,000,000 Read/Write cycles           |

## 3. Support Flash Media

### 3.1 Supported NAND Flash Type

#### 3.1.1 Small block size of 16KB

| Flash Capacity    | 128Mb | 256Mb        | 512Mb |

|-------------------|-------|--------------|-------|

| Operation Voltage |       | 2.7V to 3.6V | ,     |

Unit: Bits

#### 3.1.2 Large block size of 128KB

| Flash Capacity    | 1Gb | 2Gb  | 4Gb     | 8Gb |

|-------------------|-----|------|---------|-----|

| Operation Voltage |     | 2.7\ | to 3.6V |     |

Unit: Bits

## 3.2 Logical Format Parameters (CHS)

| Card Density*1       | 128MB       | 256MB       | 512MB       | 1GB           | 2GB           | 4GB           |

|----------------------|-------------|-------------|-------------|---------------|---------------|---------------|

| Cylinder             | 245         | 499         | 999         | 1,999         | 3,998         | 7,931         |

| Heads                | 16          | 16          | 16          | 16            | 16            | 16            |

| Sectors/Track*2      | 63          | 63          | 63          | 63            | 63            | 63            |

| Total Sectors/Card*3 | 246,960     | 502,992     | 1,006,992   | 2,014,992     | 4,029,984     | 7,994,448     |

| Capacity*4           | 127,688,704 | 256,712,704 | 514,760,704 | 1,030,848,512 | 2,061,991,936 | 4,083,580,928 |

| Card Density       | 6GB           | 8GB           | 16GB           | 32GB           | 64GB           |

|--------------------|---------------|---------------|----------------|----------------|----------------|

| Cylinder           | 11,995        | 15,863        | 16,383 16,383  |                | 16,383         |

| Heads              | 16            | 16            | 16 16          |                | 16             |

| Sectors/Track      | 63            | 63            | 63             | 63             | 63             |

| Total Sectors/Card | 12,090,960    | 15,989,904    | 16,514,064     | 16,514,064     | 16,514,064     |

| Capacity           | 6,126,062,178 | 8,168,148,992 | 16,352,280,576 | 32,704,561,152 | 65,409,122,304 |

**Unit: Bytes**

#### Notes:

- <sup>\*</sup>1. It's the logical address capacity including the area which is used for file system.

- \*2. Total tracks = number of head x number of cylinder.

- \*3. Total sector/Card = sector/track x number of head x number of cylinder.

- \*4. Those are general unformatted capacity of all cards.